Bit-Slice Design: Controllers and ALUs

by Donnamaie E. White

Copyright © 1996, 2001, 2002 Donnamaie E. White

- Pre-Introduction

- Selection of the Implementation

- Microprogramming

- Advantages of LSI

- The 2900 Family

- Language Interrelationships

- Controller Design

- Constructing the CCU

- Sequential Execution

- Multiple Sequences

- Start Addresses

- Mapping PROM

- Unconditional Branch

- Conditional Branch

- Timing Considerations

- Pipelining

- Improved Architecture

3. Adding Programming

Support to the Controller

- Expanded Testing

- Subroutines

- Nested Subroutines

- Stack Size

- Loops

- Am29811

- Am2909/11

- CASE Statement (Am29803A)

- Microprogram Memory

- Status Polling

- Interrupt Servicing

- Implementation - Interrupt Request Signals

- Vector Mapping PROM

- Next Address Control

- Am2910

- Am2910 Instructions

- Control Lines

- Interrupt Handling

- Am2914

- Interconnection of the Am2914

6. The ALU and Basic Arithmetic

- Further Enhancements

- Instruction Fields

- Instruction Set Extensions

- Sample Operations

- Arithmetic -- General

- Multiplication with the Am2901

- Am2903 Multiply

Evolution of the ALULast Edit July 11, 2001 Am2901The Am2901C is twice as fast as the original Am2901. (Each increment is used to idedicate faster, more reliable, pin compatible devices.) [Yes, there was an Am2901B. Each rev was a die-shrink.] The microinstruction control required by the Am2901 is a 9-bit field divided into 3-bit subfields. Source ControlThe selection of the operand sources via a 3-bit subfield allows the combinations shown in Table 5-5. The combinations QQ, DD were considered to occur too seldom and 00 was considered trivial. Table 5-5 Am2901 Source Selection

Function ControlThe functions allowed are the simple arithmetic and logical operations. (AMD used R and S for A and B to avoid confusion with the A and B protds of the scratchpad.) The functions selectable with a 3-bit subfield are in Table 5-6. Table 5-6 Am2901 Function Selection

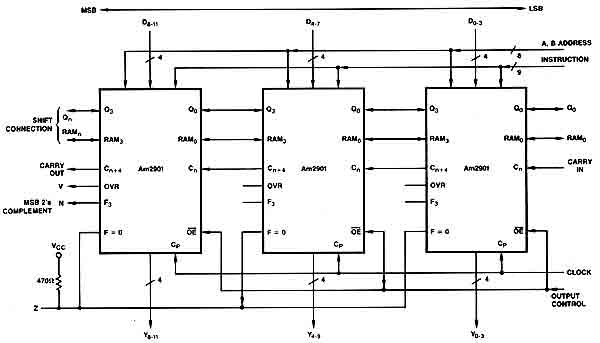

Destination ControlThe more complex control is the destination control field. The 3-bit field must select among up, down, and no shift for the RAM shift register, choose if the scratchpad memory is to be loaded, select among up, down, and no shift of the Q shift register, choose if Q is to be loaded, and select the output MUX for ALU or scratchpad. SInce some operations imply others, Table 5-7 simplifies the control selection. Table 5-7 Am2901 Destination Control InterconnectionThe Am2901 is a 4-bit slice RALU intended to two's complement arithmetic and active high data. Any number of slices may be connected to construct a CPU of any multiple of 4 bits width. Figure 5-10 shows a 12-bit CPU connected using the Cin and Cout pins in a ripple-carry configuration. Figure 5-11 shows a 16-bit CPU connected using the G and P pins of the Am2901s and an Am2902A, a carry-lookahead unit. Figure 5-10 12-Bit CPU Interconnection (ripple carry)

The execution time is considerably faster using carry-lookahead. The technique of lookahead will not be discussed further in this text at this time. Figure 5-11 16-bit CPU Interconnection (carry-lookahead)

|